下面请看2015年计算机考研:计算机组成原理试题九【附答案】

一、选择题(共20分,每题1分)

1.用户与计算机通信的界面是___B___。

A.CPU;B.外围设备;C.应用程序;D.系统程序。

2.零地址运算指令在指令格式中不给出操作数地址,它的操作数来自_C_____。

A.立即数和栈顶; B.暂存器; C.栈顶和次栈顶; D.程序计数器自动加+1。

3.水平型微指令的特点是__A____。

A.一次可以完成多个操作; B.微指令的操作控制字段不进行编码;

C.微指令的格式简短; D.微指令的格式较长。

4.有些计算机将一部分软件永恒地存于只读存储器中,称之为___C___。

A.硬件; B.软件; C.固件; D.辅助存储器。

5.主机与设备传送数据时,采用___A___,主机与设备是串行工作的。

A.程序查询方式;B.中断方式;C.DMA方式;D.通道。

6.计算机中有关ALU的描述,__D___是正确的。

A.只做算术运算,不做逻辑运算; B.只做加法; C.能存放运算结果; D.以上答案都不对。

7.所谓三总线结构的计算机是指____B__。

A.地址线、数据线和控制线三组传输线。 B.I/O总线、主存总统和 DMA总线三组传输线;

C.I/O总线、主存总线和系统总线三组传输线; D.以上都不对。

8.集中式总线控制中,__A____方式对电路故障最敏感。

A.链式查询;B.计数器定时查询;C.独立请求;D.总线式。

9.某一RAM芯片,其容量为512×8位,除电源和接地端外,该芯片引出线的最少数目是___C___。

A.21; B.17;C.19;D.20。

10.活动头磁盘存储中,信息写入或读出磁盘是__B____进行的。

A.并行方式;B.串行方式;C.串并方式;D.并串方式。

11.以下叙述__C____是正确的。

A.外部设备一旦发出中断请求,便立即得到CPU的响应;

B.外部设备一旦发出中断请求,CPU应立即响应;

C.中断方式一般用于处理随机出现的服务请求; D.程序查询用于键盘中断。

12.下列_____D_种说法有误差。

A.任何二进制整数都可用十进制表示; B.任何二进制小数都可用十进制表示;

C.任何十进制整数都可用二进制表示; D.任何十进制小数都可用二进制表示。

13.堆栈寻址方式中,设A为累加器,SP为堆栈指示器,MSP为SP指示的栈顶单元,如果进栈操作的动作顺序是(SP – 1) → SP,(A) → MSP,那么出栈操作的动作顺序应为__A___。

A.(MSP) → A,(SP) + 1 → SP; B.(SP) + l → SP,(MSP) → A;

C.(SP) – 1 → SP,(MSP) → A; D.以上都不对。

14.指令寄存器的位数取决于___B___。

A.存储器的容量; B.指令字长; C.机器字长; D.存储字长。

15.在控制器的控制方式中,机器周期内的时钟周期个数可以不相同,这属于__A____。

A.同步控制;B.异步控制;C.联合控制;D.人工控制。

16.下列叙述中___B___是正确的。

A.控制器产生的所有控制信号称为微指令;B.微程序控制器比硬连线控制器更加灵活;

C.微处理器的程序称为微程序;D.指令就是微指令。

17.CPU中的译码器主要用于_B_____ 。

A.地址译码;B.指令译码;C.选择多路数据至ALU;D.数据译码。

18.直接寻址的无条件转移指令功能是将指令中的地址码送入____A__。

A.PC; B.地址寄存器;C.累加器;D.ALU。

19.通道程序是由__B____组成。

A.I/O指令;B.通道控制字(或称通道指令);C.通道状态字;D.微程序。

20.在磁盘和磁带两种磁表面存储器中,存取时间与存储单元的物理位置有关,按存储方式分,__B___。

A.二者都是串行存取; B.磁盘是部分串行存取,磁带是串行存取;

C.磁带是部分串行存取,磁盘是串行存取; D.二者都是并行存取。

二、填空题(共20分,每题1分)

1.完成一条指令一般分为 A 周期和 B 周期,前者完成 C 操作,后者完成 D 操作。

2.常见的数据传送类指令的功能可实现 A 和 B 之间,或 C 和 D 之间的数据传送。

3.微指令格式可分为 A 型和 B 型两类,其中 C 型微指令用较长的微程序结构换取较短的微指令结构。

4.在Cache-主存的地址映象中, A 灵活性强, B 成本最高。

5.若采用硬件向量法形成中断服务程序的入口地址,则CPU在中断周期需完成 A 、

B 和 C 操作。

6.某小数定点机,字长8位(含1位符号位),当机器数分别采用原码、补码和反码时,其对应的真值范围分别是 A 、 B 、 C (均用十进制表示)。

三、名词解释(共10分,每题2分)

1.时钟周期 2.刷新 3.总线仲裁 4.机器指令 5.超流水线

四、计算题(5分)

设浮点数字长为32位,欲表示±6万的十进制数,在保证数的最大精度条件下,除阶符、数符各取1位外,阶码和尾数各取几位?按这样分配,该浮点数溢出的条件是什么?

五、简答题(共15分)

1.“在计算机中,原码和反码不能表示 -1。”这种说法是否正确,为什么?(2分)

2.除了采用高速芯片外,分别指出存储器、运算器、控制器和I/O系统各自可采用什么方法提高机器速度,各举一例简要说明。(4分)

3.异步通信与同步通信的主要区别是什么,说明通信双方如何联络。(4分)

4.在DMA方式中,CPU和DMA接口分时使用主存有几种方法?简要说明之。(5分)

六、问答题(共20分)

-

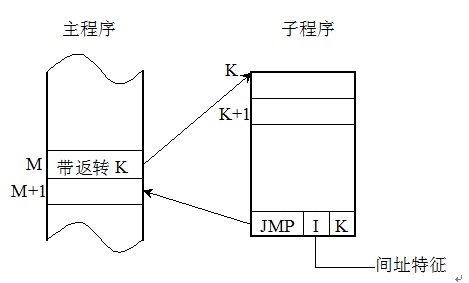

已知带返转指令的含义如下图所示,写出机器在完成带返转指令时,取指阶段和执行阶段所需的全部微操作命令及节拍安排。如果采用微程序控制,需增加哪些微操作命令?(8分)

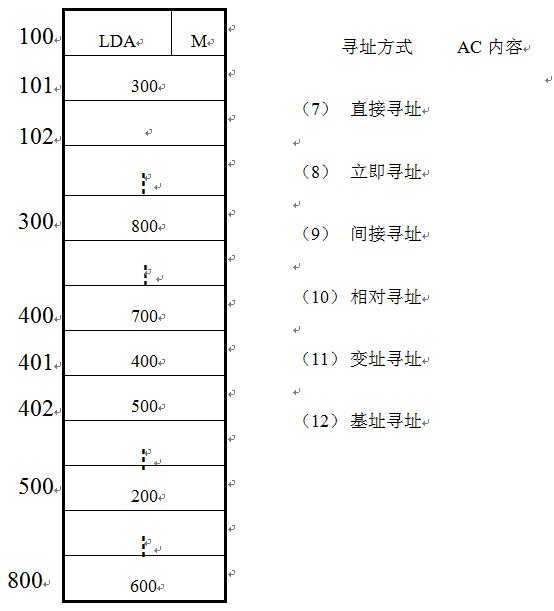

2.(6分)(指令系统 3)一条双字长的取数指令(LDA)存于存储器的100和101单元,其中第一个字为操作码和寻址特征M,第二个字为形式地址。假设PC当前值为100,变址寄存器XR的内容为100,基址寄存器的内容为200,存储器各单元的内容如下图所示。写出在下列寻址方式中,取数指令执行结束后,累加器AC的内容。

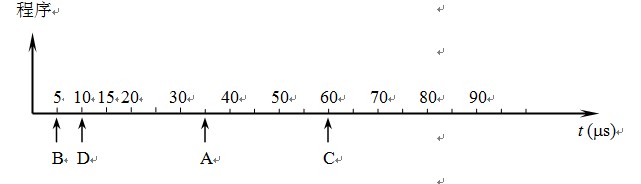

3.(6分)设某机有四个中断源A、B、C、D,其硬件排队优先次序为A > B > C > D,现要求将中断处理次序改为D > A > C > B。

(1)写出每个中断源对应的屏蔽字。

(2)按下图时间轴给出的四个中断源的请求时刻,画出CPU执行程序的轨迹。设每个中断源的中断服务程序时间均为20ms。

七、设计题(10分)

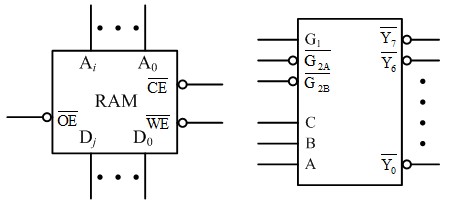

设CPU共有16根地址线和8根数据线,并用 作访存控制信号, 作读写命令信号(高电平读,低电平写)。设计一个容量为32KB,地址范围为0000H~7FFFH,且采用低位交叉编址的四体并行存储器。要求:

(1)采用下图所列芯片,详细画出CPU和存储芯片的连接图。

(2)指出图中每个存储芯片的容量及地址范围(用十六进制表示)。

实践是检验真理的唯一标准,做题时检验自身的重要途径。